|

foxBMS

1.6.0

The foxBMS Battery Management System API Documentation

|

|

foxBMS

1.6.0

The foxBMS Battery Management System API Documentation

|

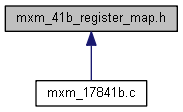

Register map of the MAX17841 bridge IC. More...

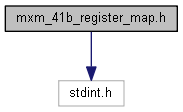

#include <stdint.h>

Go to the source code of this file.

Macros | |

| #define | MXM_BUF_CLR_TX_BUF ((MXM_41B_BUF_CMD_t)0x20u) |

| Reset transmit buffer to default state and clear TX_Q and LD_Q. More... | |

| #define | MXM_BUF_RD_MSG ((MXM_41B_BUF_CMD_t)0x91u) |

| Read receive buffer starting at RX_RD_Pointer. More... | |

| #define | MXM_BUF_RD_NXT_MSG ((MXM_41B_BUF_CMD_t)0x93u) |

| Read receive buffer starting at the oldest unread message. More... | |

| #define | MXM_BUF_WR_NXT_LD_Q_0 ((MXM_41B_BUF_CMD_t)0xB0u) |

| Select next load queue and write starting from location 0. More... | |

| #define | MXM_BUF_WR_NXT_LD_Q_1 ((MXM_41B_BUF_CMD_t)0xB2u) |

| Select next load queue and write starting from location 1. More... | |

| #define | MXM_BUF_WR_NXT_LD_Q_2 ((MXM_41B_BUF_CMD_t)0xB4u) |

| Select next load queue and write starting from location 2. More... | |

| #define | MXM_BUF_WR_NXT_LD_Q_3 ((MXM_41B_BUF_CMD_t)0xB6u) |

| Select next load queue and write starting from location 3. More... | |

| #define | MXM_BUF_WR_NXT_LD_Q_4 ((MXM_41B_BUF_CMD_t)0xB8u) |

| Select next load queue and write starting from location 4. More... | |

| #define | MXM_BUF_WR_NXT_LD_Q_5 ((MXM_41B_BUF_CMD_t)0xBAu) |

| Select next load queue and write starting from location 5. More... | |

| #define | MXM_BUF_WR_NXT_LD_Q_6 ((MXM_41B_BUF_CMD_t)0xBCu) |

| Select next load queue and write starting from location 6. More... | |

| #define | MXM_BUF_WR_LD_Q_0 ((MXM_41B_BUF_CMD_t)0xC0u) |

| Write load queue starting from location 0. More... | |

| #define | MXM_BUF_WR_LD_Q_1 ((MXM_41B_BUF_CMD_t)0xC2u) |

| Write load queue starting from location 1. More... | |

| #define | MXM_BUF_WR_LD_Q_2 ((MXM_41B_BUF_CMD_t)0xC4u) |

| Write load queue starting from location 2. More... | |

| #define | MXM_BUF_WR_LD_Q_3 ((MXM_41B_BUF_CMD_t)0xC6u) |

| Write load queue starting from location 3. More... | |

| #define | MXM_BUF_WR_LD_Q_4 ((MXM_41B_BUF_CMD_t)0xC8u) |

| Write load queue starting from location 4. More... | |

| #define | MXM_BUF_WR_LD_Q_5 ((MXM_41B_BUF_CMD_t)0xCAu) |

| Write load queue starting from location 5. More... | |

| #define | MXM_BUF_WR_LD_Q_6 ((MXM_41B_BUF_CMD_t)0xCCu) |

| Write load queue starting from location 6. More... | |

| #define | MXM_BUF_RD_LD_Q_0 ((MXM_41B_BUF_CMD_t)0xC1u) |

| Read load queue starting from location 0. More... | |

| #define | MXM_BUF_RD_LD_Q_1 ((MXM_41B_BUF_CMD_t)0xC3u) |

| Read load queue starting from location 1. More... | |

| #define | MXM_BUF_RD_LD_Q_2 ((MXM_41B_BUF_CMD_t)0xC5u) |

| Read load queue starting from location 2. More... | |

| #define | MXM_BUF_RD_LD_Q_3 ((MXM_41B_BUF_CMD_t)0xC7u) |

| Read load queue starting from location 3. More... | |

| #define | MXM_BUF_RD_LD_Q_4 ((MXM_41B_BUF_CMD_t)0xC9u) |

| Read load queue starting from location 4. More... | |

| #define | MXM_BUF_RD_LD_Q_5 ((MXM_41B_BUF_CMD_t)0xCBu) |

| Read load queue starting from location 5. More... | |

| #define | MXM_BUF_RD_LD_Q_6 ((MXM_41B_BUF_CMD_t)0xCDu) |

| Read load queue starting from location 6. More... | |

| #define | MXM_BUF_CLR_RX_BUF ((MXM_41B_BUF_CMD_t)0xE0u) |

| Reset receive buffer and pointers to default state. More... | |

| #define | MXM_REG_RX_STATUS_R ((MXM_41B_REG_ADD_t)0x01u) |

| RX status register read address. More... | |

| #define | MXM_REG_TX_STATUS_R ((MXM_41B_REG_ADD_t)0x03u) |

| TX status register read address. More... | |

| #define | MXM_REG_RX_INTERRUPT_ENABLE_R ((MXM_41B_REG_ADD_t)0x05u) |

| RX interrupt enable register read address. More... | |

| #define | MXM_REG_RX_INTERRUPT_ENABLE_W ((MXM_41B_REG_ADD_t)0x04u) |

| RX interrupt enable register write address. More... | |

| #define | MXM_REG_TX_INTERRUPT_ENABLE_R ((MXM_41B_REG_ADD_t)0x07u) |

| TX interrupt enable register read address. More... | |

| #define | MXM_REG_TX_INTERRUPT_ENABLE_W ((MXM_41B_REG_ADD_t)0x06u) |

| TX interrupt enable register write address. More... | |

| #define | MXM_REG_RX_INTERRUPT_FLAGS_R ((MXM_41B_REG_ADD_t)0x09u) |

| RX interrupt flags register read address. More... | |

| #define | MXM_REG_RX_INTERRUPT_FLAGS_W ((MXM_41B_REG_ADD_t)0x08u) |

| RX interrupt flags register write address. More... | |

| #define | MXM_REG_TX_INTERRUPT_FLAGS_R ((MXM_41B_REG_ADD_t)0x0Bu) |

| TX interrupt flags register read address. More... | |

| #define | MXM_REG_TX_INTERRUPT_FLAGS_W ((MXM_41B_REG_ADD_t)0x0Au) |

| TX interrupt flags register write address. More... | |

| #define | MXM_REG_CONFIGURATION_1_R ((MXM_41B_REG_ADD_t)0x0Du) |

| Configuration 1 register read address. More... | |

| #define | MXM_REG_CONFIGURATION_1_W ((MXM_41B_REG_ADD_t)0x0Cu) |

| Configuration 1 register write address. More... | |

| #define | MXM_REG_CONFIGURATION_2_R ((MXM_41B_REG_ADD_t)0x0Fu) |

| Configuration 2 register read address. More... | |

| #define | MXM_REG_CONFIGURATION_2_W ((MXM_41B_REG_ADD_t)0x0Eu) |

| Configuration 2 register write address. More... | |

| #define | MXM_REG_CONFIGURATION_3_R ((MXM_41B_REG_ADD_t)0x11u) |

| Configuration 3 register read address. More... | |

| #define | MXM_REG_CONFIGURATION_3_W ((MXM_41B_REG_ADD_t)0x10u) |

| Configuration 3 register write address. More... | |

| #define | MXM_REG_FMEA_R ((MXM_41B_REG_ADD_t)0x13u) |

| FMEA register read address. More... | |

| #define | MXM_REG_MODEL_R ((MXM_41B_REG_ADD_t)0x15u) |

| Model register read address. More... | |

| #define | MXM_REG_VERSION_R ((MXM_41B_REG_ADD_t)0x17u) |

| Version register read address. More... | |

| #define | MXM_REG_RX_BYTE_R ((MXM_41B_REG_ADD_t)0x19u) |

| RX byte register read address. More... | |

| #define | MXM_REG_RX_SPACE_R ((MXM_41B_REG_ADD_t)0x1Bu) |

| RX space register read address. More... | |

| #define | MXM_REG_TX_QUEUE_SELECTS_R ((MXM_41B_REG_ADD_t)0x95u) |

| TX queue selects register read address. More... | |

| #define | MXM_REG_RX_READ_POINTER_R ((MXM_41B_REG_ADD_t)0x97u) |

| RX read pointer register read address. More... | |

| #define | MXM_REG_RX_WRITE_POINTER_R ((MXM_41B_REG_ADD_t)0x99u) |

| RX write pointer register read address. More... | |

| #define | MXM_REG_RX_NEXT_MESSAGE_R ((MXM_41B_REG_ADD_t)0x9Bu) |

| RX next message register read address. More... | |

Typedefs | |

| typedef uint8_t | MXM_41B_BUF_CMD_t |

| Type for MAX17841B buffer transaction commands. More... | |

| typedef uint8_t | MXM_41B_REG_ADD_t |

| MAX17841B register addresses. More... | |

Register map of the MAX17841 bridge IC.

SPDX-License-Identifier: BSD-3-Clause

Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

We kindly request you to use one or more of the following phrases to refer to foxBMS in your hardware, software, documentation or advertising materials:

Definition in file mxm_41b_register_map.h.

| #define MXM_BUF_CLR_RX_BUF ((MXM_41B_BUF_CMD_t)0xE0u) |

Reset receive buffer and pointers to default state.

Definition at line 204 of file mxm_41b_register_map.h.

| #define MXM_BUF_CLR_TX_BUF ((MXM_41B_BUF_CMD_t)0x20u) |

Reset transmit buffer to default state and clear TX_Q and LD_Q.

Definition at line 84 of file mxm_41b_register_map.h.

| #define MXM_BUF_RD_LD_Q_0 ((MXM_41B_BUF_CMD_t)0xC1u) |

Read load queue starting from location 0.

Definition at line 169 of file mxm_41b_register_map.h.

| #define MXM_BUF_RD_LD_Q_1 ((MXM_41B_BUF_CMD_t)0xC3u) |

Read load queue starting from location 1.

Definition at line 174 of file mxm_41b_register_map.h.

| #define MXM_BUF_RD_LD_Q_2 ((MXM_41B_BUF_CMD_t)0xC5u) |

Read load queue starting from location 2.

Definition at line 179 of file mxm_41b_register_map.h.

| #define MXM_BUF_RD_LD_Q_3 ((MXM_41B_BUF_CMD_t)0xC7u) |

Read load queue starting from location 3.

Definition at line 184 of file mxm_41b_register_map.h.

| #define MXM_BUF_RD_LD_Q_4 ((MXM_41B_BUF_CMD_t)0xC9u) |

Read load queue starting from location 4.

Definition at line 189 of file mxm_41b_register_map.h.

| #define MXM_BUF_RD_LD_Q_5 ((MXM_41B_BUF_CMD_t)0xCBu) |

Read load queue starting from location 5.

Definition at line 194 of file mxm_41b_register_map.h.

| #define MXM_BUF_RD_LD_Q_6 ((MXM_41B_BUF_CMD_t)0xCDu) |

Read load queue starting from location 6.

Definition at line 199 of file mxm_41b_register_map.h.

| #define MXM_BUF_RD_MSG ((MXM_41B_BUF_CMD_t)0x91u) |

Read receive buffer starting at RX_RD_Pointer.

Definition at line 89 of file mxm_41b_register_map.h.

| #define MXM_BUF_RD_NXT_MSG ((MXM_41B_BUF_CMD_t)0x93u) |

Read receive buffer starting at the oldest unread message.

Definition at line 94 of file mxm_41b_register_map.h.

| #define MXM_BUF_WR_LD_Q_0 ((MXM_41B_BUF_CMD_t)0xC0u) |

Write load queue starting from location 0.

Definition at line 134 of file mxm_41b_register_map.h.

| #define MXM_BUF_WR_LD_Q_1 ((MXM_41B_BUF_CMD_t)0xC2u) |

Write load queue starting from location 1.

Definition at line 139 of file mxm_41b_register_map.h.

| #define MXM_BUF_WR_LD_Q_2 ((MXM_41B_BUF_CMD_t)0xC4u) |

Write load queue starting from location 2.

Definition at line 144 of file mxm_41b_register_map.h.

| #define MXM_BUF_WR_LD_Q_3 ((MXM_41B_BUF_CMD_t)0xC6u) |

Write load queue starting from location 3.

Definition at line 149 of file mxm_41b_register_map.h.

| #define MXM_BUF_WR_LD_Q_4 ((MXM_41B_BUF_CMD_t)0xC8u) |

Write load queue starting from location 4.

Definition at line 154 of file mxm_41b_register_map.h.

| #define MXM_BUF_WR_LD_Q_5 ((MXM_41B_BUF_CMD_t)0xCAu) |

Write load queue starting from location 5.

Definition at line 159 of file mxm_41b_register_map.h.

| #define MXM_BUF_WR_LD_Q_6 ((MXM_41B_BUF_CMD_t)0xCCu) |

Write load queue starting from location 6.

Definition at line 164 of file mxm_41b_register_map.h.

| #define MXM_BUF_WR_NXT_LD_Q_0 ((MXM_41B_BUF_CMD_t)0xB0u) |

Select next load queue and write starting from location 0.

Definition at line 99 of file mxm_41b_register_map.h.

| #define MXM_BUF_WR_NXT_LD_Q_1 ((MXM_41B_BUF_CMD_t)0xB2u) |

Select next load queue and write starting from location 1.

Definition at line 104 of file mxm_41b_register_map.h.

| #define MXM_BUF_WR_NXT_LD_Q_2 ((MXM_41B_BUF_CMD_t)0xB4u) |

Select next load queue and write starting from location 2.

Definition at line 109 of file mxm_41b_register_map.h.

| #define MXM_BUF_WR_NXT_LD_Q_3 ((MXM_41B_BUF_CMD_t)0xB6u) |

Select next load queue and write starting from location 3.

Definition at line 114 of file mxm_41b_register_map.h.

| #define MXM_BUF_WR_NXT_LD_Q_4 ((MXM_41B_BUF_CMD_t)0xB8u) |

Select next load queue and write starting from location 4.

Definition at line 119 of file mxm_41b_register_map.h.

| #define MXM_BUF_WR_NXT_LD_Q_5 ((MXM_41B_BUF_CMD_t)0xBAu) |

Select next load queue and write starting from location 5.

Definition at line 124 of file mxm_41b_register_map.h.

| #define MXM_BUF_WR_NXT_LD_Q_6 ((MXM_41B_BUF_CMD_t)0xBCu) |

Select next load queue and write starting from location 6.

Definition at line 129 of file mxm_41b_register_map.h.

| #define MXM_REG_CONFIGURATION_1_R ((MXM_41B_REG_ADD_t)0x0Du) |

Configuration 1 register read address.

Definition at line 259 of file mxm_41b_register_map.h.

| #define MXM_REG_CONFIGURATION_1_W ((MXM_41B_REG_ADD_t)0x0Cu) |

Configuration 1 register write address.

Definition at line 264 of file mxm_41b_register_map.h.

| #define MXM_REG_CONFIGURATION_2_R ((MXM_41B_REG_ADD_t)0x0Fu) |

Configuration 2 register read address.

Definition at line 269 of file mxm_41b_register_map.h.

| #define MXM_REG_CONFIGURATION_2_W ((MXM_41B_REG_ADD_t)0x0Eu) |

Configuration 2 register write address.

Definition at line 274 of file mxm_41b_register_map.h.

| #define MXM_REG_CONFIGURATION_3_R ((MXM_41B_REG_ADD_t)0x11u) |

Configuration 3 register read address.

Definition at line 279 of file mxm_41b_register_map.h.

| #define MXM_REG_CONFIGURATION_3_W ((MXM_41B_REG_ADD_t)0x10u) |

Configuration 3 register write address.

Definition at line 284 of file mxm_41b_register_map.h.

| #define MXM_REG_FMEA_R ((MXM_41B_REG_ADD_t)0x13u) |

FMEA register read address.

Definition at line 289 of file mxm_41b_register_map.h.

| #define MXM_REG_MODEL_R ((MXM_41B_REG_ADD_t)0x15u) |

Model register read address.

Definition at line 294 of file mxm_41b_register_map.h.

| #define MXM_REG_RX_BYTE_R ((MXM_41B_REG_ADD_t)0x19u) |

RX byte register read address.

Definition at line 304 of file mxm_41b_register_map.h.

| #define MXM_REG_RX_INTERRUPT_ENABLE_R ((MXM_41B_REG_ADD_t)0x05u) |

RX interrupt enable register read address.

Definition at line 219 of file mxm_41b_register_map.h.

| #define MXM_REG_RX_INTERRUPT_ENABLE_W ((MXM_41B_REG_ADD_t)0x04u) |

RX interrupt enable register write address.

Definition at line 224 of file mxm_41b_register_map.h.

| #define MXM_REG_RX_INTERRUPT_FLAGS_R ((MXM_41B_REG_ADD_t)0x09u) |

RX interrupt flags register read address.

Definition at line 239 of file mxm_41b_register_map.h.

| #define MXM_REG_RX_INTERRUPT_FLAGS_W ((MXM_41B_REG_ADD_t)0x08u) |

RX interrupt flags register write address.

Definition at line 244 of file mxm_41b_register_map.h.

| #define MXM_REG_RX_NEXT_MESSAGE_R ((MXM_41B_REG_ADD_t)0x9Bu) |

RX next message register read address.

Definition at line 329 of file mxm_41b_register_map.h.

| #define MXM_REG_RX_READ_POINTER_R ((MXM_41B_REG_ADD_t)0x97u) |

RX read pointer register read address.

Definition at line 319 of file mxm_41b_register_map.h.

| #define MXM_REG_RX_SPACE_R ((MXM_41B_REG_ADD_t)0x1Bu) |

RX space register read address.

Definition at line 309 of file mxm_41b_register_map.h.

| #define MXM_REG_RX_STATUS_R ((MXM_41B_REG_ADD_t)0x01u) |

RX status register read address.

Definition at line 209 of file mxm_41b_register_map.h.

| #define MXM_REG_RX_WRITE_POINTER_R ((MXM_41B_REG_ADD_t)0x99u) |

RX write pointer register read address.

Definition at line 324 of file mxm_41b_register_map.h.

| #define MXM_REG_TX_INTERRUPT_ENABLE_R ((MXM_41B_REG_ADD_t)0x07u) |

TX interrupt enable register read address.

Definition at line 229 of file mxm_41b_register_map.h.

| #define MXM_REG_TX_INTERRUPT_ENABLE_W ((MXM_41B_REG_ADD_t)0x06u) |

TX interrupt enable register write address.

Definition at line 234 of file mxm_41b_register_map.h.

| #define MXM_REG_TX_INTERRUPT_FLAGS_R ((MXM_41B_REG_ADD_t)0x0Bu) |

TX interrupt flags register read address.

Definition at line 249 of file mxm_41b_register_map.h.

| #define MXM_REG_TX_INTERRUPT_FLAGS_W ((MXM_41B_REG_ADD_t)0x0Au) |

TX interrupt flags register write address.

Definition at line 254 of file mxm_41b_register_map.h.

| #define MXM_REG_TX_QUEUE_SELECTS_R ((MXM_41B_REG_ADD_t)0x95u) |

TX queue selects register read address.

Definition at line 314 of file mxm_41b_register_map.h.

| #define MXM_REG_TX_STATUS_R ((MXM_41B_REG_ADD_t)0x03u) |

TX status register read address.

Definition at line 214 of file mxm_41b_register_map.h.

| #define MXM_REG_VERSION_R ((MXM_41B_REG_ADD_t)0x17u) |

Version register read address.

Definition at line 299 of file mxm_41b_register_map.h.

| typedef uint8_t MXM_41B_BUF_CMD_t |

Type for MAX17841B buffer transaction commands.

SPI commands for buffer transactions of the MAX17841B.

Definition at line 67 of file mxm_41b_register_map.h.

| typedef uint8_t MXM_41B_REG_ADD_t |

MAX17841B register addresses.

Register addresses for the MAX17841B. Valid register addresses range from 0x01 to 0x1B and 0x95 to 0x9B Odd addresses are read addresses and even addresses are write addresses. Read-only registers have no write address.

Definition at line 78 of file mxm_41b_register_map.h.