|

foxBMS

1.6.0

The foxBMS Battery Management System API Documentation

|

|

foxBMS

1.6.0

The foxBMS Battery Management System API Documentation

|

Headers for the configuration for the SPI module. More...

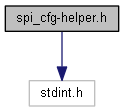

#include <stdint.h>

Go to the source code of this file.

Macros | |

| #define | SPI_HARDWARE_CHIP_SELECT_ACTIVE (0u) |

| #define | SPI_HARDWARE_CHIP_SELECT_NOT_ACTIVE (1u) |

| #define | SPI_HARDWARE_CHIP_SELECT_DISABLE_ALL |

| #define | SPI_HARDWARE_CHIP_SELECT_0_ACTIVE |

| #define | SPI_HARDWARE_CHIP_SELECT_1_ACTIVE |

| #define | SPI_HARDWARE_CHIP_SELECT_2_ACTIVE |

| #define | SPI_HARDWARE_CHIP_SELECT_3_ACTIVE |

| #define | SPI_HARDWARE_CHIP_SELECT_4_ACTIVE |

| #define | SPI_HARDWARE_CHIP_SELECT_5_ACTIVE |

| #define | SPI_HARDWARE_CHIP_SELECT_0_BIT_POSITION (0u) |

| #define | SPI_HARDWARE_CHIP_SELECT_1_BIT_POSITION (1u) |

| #define | SPI_HARDWARE_CHIP_SELECT_2_BIT_POSITION (2u) |

| #define | SPI_HARDWARE_CHIP_SELECT_3_BIT_POSITION (3u) |

| #define | SPI_HARDWARE_CHIP_SELECT_4_BIT_POSITION (4u) |

| #define | SPI_HARDWARE_CHIP_SELECT_5_BIT_POSITION (5u) |

Headers for the configuration for the SPI module.

SPDX-License-Identifier: BSD-3-Clause

Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

We kindly request you to use one or more of the following phrases to refer to foxBMS in your hardware, software, documentation or advertising materials:

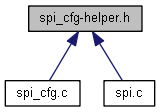

Definition in file spi_cfg-helper.h.

| #define SPI_HARDWARE_CHIP_SELECT_0_ACTIVE |

Definition at line 95 of file spi_cfg-helper.h.

| #define SPI_HARDWARE_CHIP_SELECT_0_BIT_POSITION (0u) |

HW chip select bit position, TMS570LC4357 has maximum of six hardware chip select pins per SPI node

Definition at line 65 of file spi_cfg-helper.h.

| #define SPI_HARDWARE_CHIP_SELECT_1_ACTIVE |

Definition at line 109 of file spi_cfg-helper.h.

| #define SPI_HARDWARE_CHIP_SELECT_1_BIT_POSITION (1u) |

HW chip select bit position, TMS570LC4357 has maximum of six hardware chip select pins per SPI node

Definition at line 66 of file spi_cfg-helper.h.

| #define SPI_HARDWARE_CHIP_SELECT_2_ACTIVE |

Definition at line 123 of file spi_cfg-helper.h.

| #define SPI_HARDWARE_CHIP_SELECT_2_BIT_POSITION (2u) |

HW chip select bit position, TMS570LC4357 has maximum of six hardware chip select pins per SPI node

Definition at line 67 of file spi_cfg-helper.h.

| #define SPI_HARDWARE_CHIP_SELECT_3_ACTIVE |

Definition at line 137 of file spi_cfg-helper.h.

| #define SPI_HARDWARE_CHIP_SELECT_3_BIT_POSITION (3u) |

HW chip select bit position, TMS570LC4357 has maximum of six hardware chip select pins per SPI node

Definition at line 68 of file spi_cfg-helper.h.

| #define SPI_HARDWARE_CHIP_SELECT_4_ACTIVE |

Definition at line 151 of file spi_cfg-helper.h.

| #define SPI_HARDWARE_CHIP_SELECT_4_BIT_POSITION (4u) |

HW chip select bit position, TMS570LC4357 has maximum of six hardware chip select pins per SPI node

Definition at line 69 of file spi_cfg-helper.h.

| #define SPI_HARDWARE_CHIP_SELECT_5_ACTIVE |

Definition at line 165 of file spi_cfg-helper.h.

| #define SPI_HARDWARE_CHIP_SELECT_5_BIT_POSITION (5u) |

HW chip select bit position, TMS570LC4357 has maximum of six hardware chip select pins per SPI node

Definition at line 70 of file spi_cfg-helper.h.

| #define SPI_HARDWARE_CHIP_SELECT_ACTIVE (0u) |

Bit mask to activate hardware chip select in the CSNR field of the SPIDAT1 register

Definition at line 74 of file spi_cfg-helper.h.

| #define SPI_HARDWARE_CHIP_SELECT_DISABLE_ALL |

Definition at line 81 of file spi_cfg-helper.h.

| #define SPI_HARDWARE_CHIP_SELECT_NOT_ACTIVE (1u) |

Bit mask to not activate hardware chip select in the CSNR field of the SPIDAT1 register

Definition at line 77 of file spi_cfg-helper.h.