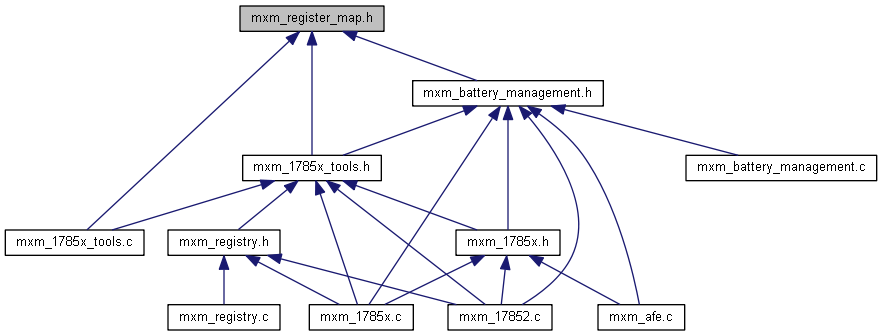

MAX1785x register names.

Register names and addresses of the monitoring ICs MAX17852 and MAX17853. Please note that the MAX17853 only supports a subset of these register values.

| Enumerator |

|---|

| MXM_REG_VERSION | VERSION is a read only accessible register which returns information on the device

|

| MXM_REG_ADDRESS | ADDRESS is a read and write accessible register which sets the first, last, and device address used by a device in a UART chain (UARTSEL=1). This register has no effect on a device operating in SPI mode (UARTSEL=0).

|

| MXM_REG_STATUS1 | STATUS1 is a read and write accessible register which relates the current status of the device. STATUS1 also contains summary information on STATUS2, STATUS3, and FMEA registers, and other selected registers indicating if additional read back checks are required.

|

| MXM_REG_STATUS2 | STATUS2 is a read and write accessible register which contains summary information on alerts related to interface and communication faults.

|

| MXM_REG_STATUS3 | STATUS3 is a read and write accessible register which contains summary information on alerts related to automated cell balancing operations.

|

| MXM_REG_FMEA1 | FMEA1 is a read and write accessible register which relates current information on possible fault conditions.

|

| MXM_REG_FMEA2 | FMEA2 is a read and write accessible register which relates current information on possible fault conditions.

|

| MXM_REG_ALRTSUM | ALRTSUM is a read accessible register which relates added, detailed information on the current states of the device, breaking out several summary bits in STATUS1.

|

| MXM_REG_ALRTOVCELL | ALRTOVCELL is a read accessible register which relates current information on cell over voltage fault alerts based on ADC measurements.

|

| MXM_REG_ALRTUVCELL | ALRTUVCELL is a read accessible register which relates current information on cell under voltage fault alerts based on ADC measurements.

|

| MXM_REG_MINMAXCELL | MINMAX is a read accessible register which relates the cell locations with the highest and lowest values measured.

|

| MXM_REG_ALRTAUXPRTCT | ALRTAUXPRTCT is a read accessible register which relates current information on auxiliary input protection fault alerts.

|

| MXM_REG_ALRTAUXOV | ALRTAUXOV is a read accessible register which relates current information on auxiliary over voltage (cold) fault alerts.

|

| MXM_REG_ALRTAUXUV | ALRTAUXUV is a read accessible register which relates current information on auxiliary under voltage fault (hot) alerts.

|

| MXM_REG_ALRTCOMPOV | ALRTCOMPOV is a read accessible register which relates current information on cell over voltage fault alerts based on the redundant comparator.

|

| MXM_REG_ALRTCOMPUV | ALRTCOMPUV is a read accessible register which relates current information on cell under voltage fault alerts based on the redundant comparator.

|

| MXM_REG_ALRTCOMPAUXOV | ALRTCOMPAUXOV is a read accessible register which relates current information on auxiliary over voltage fault (cold) alerts based on the redundant comparator.

|

| MXM_REG_ALRTCOMPAUXUV | ALRTCOMPAUXUV is a read accessible register which relates current information on auxiliary under voltage fault (hot) alerts based on the redundant comparator.

|

| MXM_REG_ALRTBALSW | ALRTBALSW is a read accessible register which relates current summary information on balancing switch fault alerts.

|

| MXM_REG_SWACTION | SWACTION is a read and write accessible register which contains bits allowing software exit and reset requests. These requests are not recommended for general use, but may be of use in case of error.

|

| MXM_REG_DEVCFG1 | DEVCFG1 is a read and write accessible register which governs the configuration of the device interface operation.

|

| MXM_REG_DEVCFG2 | DEVCFG2 is a read and write accessible register which governs the configuration of the device filtering, several top level diagnostic modes, and timeout monitors.

|

| MXM_REG_AUXGPIOCFG | AUXGPIOCFG is a read and write accessible register which governs the configuration of the AUX/GPIO multifunction pins.

|

| MXM_REG_GPIOCFG | GPIOCFG is a read and write accessible register which governs the output state of GPIO outputs and reads back the input state of GPIO inputs.

|

| MXM_REG_PACKCFG | PACKCFG is a read and write accessible register which configures the part such that the top most cell and block used in the application is known. Details of Flex Pack applications are also configured within this register.

|

| MXM_REG_ALRTIRQEN | ALRTIRQEN is a read and write accessible register which selects which STATS1 alerts trigger interrupts via the ALERT interface port(s), and are included in the DCByte and Alert Packet (UART) or ALERT bit (SPI) notifications. Note the information in the STATUS1 register itself (or any component terms rolled up into STATUS1) is not masked/disabled by these settings, allowing the underlying data to always be available via STATUS1 readback.

|

| MXM_REG_ALRTOVEN | ALRTOVEN is a read and write accessible register which enables over voltage fault checks on selected input channels during scans using either the ADC or Comparator.

|

| MXM_REG_ALRTUVEN | ALRTUVEN is a read and write accessible register which enables under voltage fault checks on selected input channels during scans using either the ADC or Comparator.

|

| MXM_REG_ALRTAUXOVEN | ALRTAUXOVEN is a read and write accessible register which enables auxiliary over voltage (cold) fault checks on selected Auxiliary channels during scans using either the ADC or Comparator.

|

| MXM_REG_ALRTAUXUVEN | ALRTAUXUVEN is a read and write accessible register which enables auxiliary under voltage (hot) fault checks on selected Auxiliary channels using either the ADC or Comparator.

|

| MXM_REG_ALRTCALTST | ALRTCALTST is a read and write accessible register which allows the user to force Calibration alerts to test readback and interrupt logic. The forced alert(s) will remain forced until this register is written back to zeros (assuming the existing calibration data is within range)

|

| MXM_REG_OVTHCLR | OVTHCLR is a read and write accessible register which selects the cell over voltage alert clear threshold used with unipolar ADC measurements.

|

| MXM_REG_OVTHSET | OVTHSET is a read and write accessible register which selects the cell over voltage alert set threshold used with unipolar ADC measurements.

|

| MXM_REG_UVTHCLR | UVTHCLR is a read and write accessible register which selects the cell under voltage alert clear threshold used with unipolar ADC measurements.

|

| MXM_REG_UVTHSET | UVTHSET is a read and write accessible register which selects the cell under voltage alert set threshold used with unipolar ADC measurements.

|

| MXM_REG_MSMTCH | MSMTCH is a read and write accessible register which selects the cell voltage mismatch alert threshold used with ADC cell scan measurements.

|

| MXM_REG_BIPOVTHCLR | BIPOVTHCLR is a read and write accessible register which selects the cell over voltage alert clear threshold used with bipolar ADC measurements.

|

| MXM_REG_BIPOVTHSET | BIPOVTHSET is a read and write accessible register which selects the cell over voltage alert set threshold used with bipolar ADC measurements.

|

| MXM_REG_BIPUVTHCLR | BIPUVTHCLR is a read and write accessible register which selects the cell under voltage alert clear threshold used with bipolar ADC measurements.

|

| MXM_REG_BIPUVTHSET | BIPUVTHSET is a read and write accessible register which selects the cell under voltage alert set threshold used with bipolar ADC measurements.

|

| MXM_REG_BLKOVTHCLR | BLKOVTHCLR is a read and write accessible register which selects the block over voltage alert clear threshold used with ADC measurements.

|

| MXM_REG_BLKOVTHSET | BLKOVTHSET is a read and write accessible register which selects the block over voltage alert set threshold used with ADC measurements.

|

| MXM_REG_BLKUVTHCLR | BLKUVTHCLR is a read and write accessible register which selects the block under voltage alert clear threshold used with ADC measurements.

|

| MXM_REG_BLKUVTHSET | BLKUVTHSET is a read and write accessible register which selects the block under voltage alert set threshold used with ADC measurements.

|

| MXM_REG_CSAOVTHCLR | MAX17852 only: CSAOVTHCLR is a read and write accessible register which selects the CSA over voltage alert clear threshold used with ADC measurements.

|

| MXM_REG_CSAOVTHSET | MAX17852 only: CSAOVTHSET is a read and write accessible register which selects the CSA over voltage alert set threshold used with ADC measurements.

|

| MXM_REG_CSAUVTHCLR | MAX17852 only: CSAUVTHCLR is a read and write accessible register which selects the CSA under voltage alert clear threshold used with ADC measurements.

|

| MXM_REG_CSAUVTHSET | MAX17852 only: CSAUVTHSET is a read and write accessible register which selects the CSA under voltage alert set threshold used with ADC measurements.

|

| MXM_REG_AUXROVTHCLR | AUXROVTHCLR is a read and write accessible register which selects the over voltage (cold) alert clear threshold used with Ratiometric Auxiliary ADC measurements.

|

| MXM_REG_AUXROVTHSET | AUXROVTHSET is a read and write accessible register which selects the over voltage (cold) alert set threshold used with Ratiometric Auxiliary ADC measurements.

|

| MXM_REG_AUXRUVTHCLR | AUXRUVTHCLR is a read and write accessible register which selects the under voltage (hot) alert clear threshold used with Ratiometric Auxiliary ADC measurements.

|

| MXM_REG_AUXRUVTHSET | AUXRUVTHSET is a read and write accessible register which selects the under voltage (hot) alert set threshold used with Ratiometric Auxiliary ADC measurements.

|

| MXM_REG_AUXOVTHCLR | AUXOVTHCLR is a read and write accessible register which selects the over voltage alert clear threshold used with Absolute Auxiliary ADC measurements.

|

| MXM_REG_AUXAOVTHSET | AUXAOVTHSET is a read and write accessible register which selects the over voltage alert set threshold used with Absolute Auxiliary ADC measurements.

|

| MXM_REG_AUXAUVTHCLR | AUXAUVTHCLR is a read and write accessible register which selects the under voltage alert clear threshold used with Absolute Auxiliary ADC measurements.

|

| MXM_REG_AUXAUVTHSET | AUXAUVTHSET is a read and write accessible register which selects the under voltage alert set threshold used with Absolute Auxiliary ADC measurements.

|

| MXM_REG_COMPOVTH | COMPOVTH is a read and write accessible register which selects the cell over voltage alert threshold for the redundant comparator.

|

| MXM_REG_COMPUVTH | COMPUVTH is a read and write accessible register which selects the cell under voltage alert threshold for the redundant comparator.

|

| MXM_REG_COMPAUXROVTH | COMPAUXROVTH is a read and write accessible register which selects the over voltage (cold) alert threshold applied during Ratiometric Auxiliary comparator measurements.

|

| MXM_REG_COMPAUXRUVTH | COMPAUXRUVTH is a read and write accessible register which selects the under voltage (hot) alert threshold applied during Ratiometric Auxiliary comparator measurements.

|

| MXM_REG_COMPAUXAOVTH | COMPAUXAOVTH is a read and write accessible register which selects the over voltage alert threshold applied during Absolute Auxiliary comparator measurements.

|

| MXM_REG_COMPAUXAUVTH | COMPAUXAUVTH is a read and write accessible register which selects the under voltage alert threshold applied during Absolute Auxiliary comparator measurements.

|

| MXM_REG_COMPOPNTH | COMPOPNTH is a read and write accessible register which selects the under voltage alert threshold applied to Unipolar Cell inputs in Open Diagnostic Mode.

|

| MXM_REG_COMPAUXROPNTH | COMPAUXROPNTH is a read and write accessible register which selects the under voltage alert threshold applied to Ratiometric Auxiliary inputs in Open Diagnostic Mode.

|

| MXM_REG_COMPAUXAOPNTH | COMPAUXAOPNTH is a read and write accessible register which selects the under voltage alert threshold applied to Absolute Auxiliary inputs in Open Diagnostic Mode.

|

| MXM_REG_COMPACCOVTH | COMPACCOVTH is a read and write accessible register which selects the over voltage alert threshold applied during comparator accuracy diagnostics.

|

| MXM_REG_COMPACCUVTH | COMPACCUVTH is a read and write accessible register which selects the under voltage alert threshold applied during comparator accuracy diagnostics.

|

| MXM_REG_BALSHRTTHR | BALSHRTTHR is a read and write accessible register which selects alert threshold used during the Balance Switch Short Diagnostic mode.

|

| MXM_REG_BALLOWTHR | BALLOWTHR is a read and write accessible register which selects alert low threshold used during the Balance Switch Open Diagnostic Mode.

|

| MXM_REG_BALHIGHTHR | BALHIGHTHR is a read and write accessible register which selects alert High threshold used during the Balance Switch Open Diagnostic mode.

|

| MXM_REG_CSA | MAX17852 only: CSA is a read accessible register which holds the current value for each enabled individual auxiliary measurement result.

|

| MXM_REG_CELL1 | CELLn is a read accessible register which holds the current value for each individual cell measurement result.

|

| MXM_REG_CELL2 | CELLn is a read accessible register which holds the current value for each individual cell measurement result.

|

| MXM_REG_CELL3 | CELLn is a read accessible register which holds the current value for each individual cell measurement result.

|

| MXM_REG_CELL4 | CELLn is a read accessible register which holds the current value for each individual cell measurement result.

|

| MXM_REG_CELL5 | CELLn is a read accessible register which holds the current value for each individual cell measurement result.

|

| MXM_REG_CELL6 | CELLn is a read accessible register which holds the current value for each individual cell measurement result.

|

| MXM_REG_CELL7 | CELLn is a read accessible register which holds the current value for each individual cell measurement result.

|

| MXM_REG_CELL8 | CELLn is a read accessible register which holds the current value for each individual cell measurement result.

|

| MXM_REG_CELL9 | CELLn is a read accessible register which holds the current value for each individual cell measurement result.

|

| MXM_REG_CELL10 | CELLn is a read accessible register which holds the current value for each individual cell measurement result.

|

| MXM_REG_CELL11 | CELLn is a read accessible register which holds the current value for each individual cell measurement result.

|

| MXM_REG_CELL12 | CELLn is a read accessible register which holds the current value for each individual cell measurement result.

|

| MXM_REG_CELL13 | CELLn is a read accessible register which holds the current value for each individual cell measurement result.

|

| MXM_REG_CELL14 | CELLn is a read accessible register which holds the current value for each individual cell measurement result.

|

| MXM_REG_BLOCK | BLOCK is a read accessible register which holds the current value for the total block measurement result.

|

| MXM_REG_TOTAL | TOTAL is a read accessible register which holds the current value for the sum of all enabled measurement results within the stack.

|

| MXM_REG_DIAG1 | DIAG1 is a read-only register which contains the Diagnostic result requested by the DIAGCFG:DIAGSEL1 selection taken during the last ADC acquisition.

|

| MXM_REG_DIAG2 | DIAG2 is a read-only register which contains the Diagnostic result requested by the DIAGCFG:DIAGSEL2 selection taken during the last ADC acquisition.

|

| MXM_REG_AUX0 | AUXn is a read accessible register which holds the current value for each enabled individual auxiliary measurement result.

|

| MXM_REG_AUX1 | AUXn is a read accessible register which holds the current value for each enabled individual auxiliary measurement result.

|

| MXM_REG_AUX2 | AUXn is a read accessible register which holds the current value for each enabled individual auxiliary measurement result.

|

| MXM_REG_AUX3 | AUXn is a read accessible register which holds the current value for each enabled individual auxiliary measurement result.

|

| MXM_REG_AUX4 | MAX17853 only: AUXn is a read accessible register which holds the current value for each enabled individual auxiliary measurement result.

|

| MXM_REG_AUX5 | MAX17853 only: AUXn is a read accessible register which holds the current value for each enabled individual auxiliary measurement result.

|

| MXM_REG_POLARITYCTRL | POLARITYCTRL is a read and write accessible register which governs the measurement type used during scans. In general, Unipolar mode indicates a Cell and Bipolar mode indicates a Bus-Bar.

|

| MXM_REG_AUXREFCTRL | AUXREFCTRL is a read and write accessible register which governs the reference range used for enabled Auxiliary channels during ADC and COMP acquisition sequences.

|

| MXM_REG_AUXTIME | AUXTIME is a read and write accessible register which governs the setting time allowed for biasing AUX/GPIO pins prior to measurements.

|

| MXM_REG_ACQCFG | ACQCFG is a read and write accessible register which governs several aspects of the measurement and acquisition procedure.

|

| MXM_REG_BALSWDLY | BALSWDLY is a read and write accessible register which selects the delay intervals used within Manual and Automated Cell Balancing operations when ADC measurements are requested.

|

| MXM_REG_MEASUREEN1 | MEASUREEN1 is a read and write accessible register which governs the channels measured during ADC and COMP acquisition sequences.

|

| MXM_REG_MEASUREEN2 | MEASUREEN2 is a read and write accessible register which governs the auxiliary channels measured during ADC and COMP acquisition sequences, as well as IIR initialization.

|

| MXM_REG_SCANCTRL | SCANCTRL is a read and write accessible register which governs the internal measurement acquisitions (scan) requested of the device. The register also manages the handling of data generated as a result of any scan request.

ADC Scans are used for precision measurements of cell and auxiliary voltages.

COMP Scans are used for periodic safety/redundancy checking of ADC results, and in some cases, enhanced communication efficiency.

On Demand Calibration will run an internal calibration of the ADC and update the Calibration Data Registers. All ADC measurements requested by Scan and Diagnostic Configuration and Control settings will be ignored.

Balance Switch and Cell Sense Wire Open ADC Diagnostic Scans are a special class of ADC Scan. Use of these settings temporarily overrides other Scan and Diagnostic Configuration and Control settings. See BALSW and Cell Sense Wire Diagnostics for details.

|

| MXM_REG_ADCTEST1A | ADCTEST1A is a read and write accessible register which contains user specified arguments used in ALU Diagnostics.

|

| MXM_REG_ADCTEST1B | ADCTEST1B is a read and write accessible register which contains user specified arguments used in ALU Diagnostics.

|

| MXM_REG_ADCTEST2A | ADCTEST2A is a read and write accessible register which contains user specified arguments used in ALU Diagnostics.

|

| MXM_REG_ADCTEST2B | ADCTEST2B is a read and write accessible register which contains user specified arguments used in ALU Diagnostics.

|

| MXM_REG_DIAGCFG | DIAGCFG is a read and write accessible register which governs diagnostic source and mode options applied to the internal measurement acquisitions (scans).

|

| MXM_REG_CTSTCFG | CTSTCFG is a read and write accessible register which controls the application of diagnostic current sources to selected cell input channels.

|

| MXM_REG_AUXSTCFG | AUXSTCFG is a read and write accessible register which controls the application of diagnostic modes and current source to selected Auxiliary and/or CSA input channels.

|

| MXM_REG_DIAGGENCFG | DIAGGENCFG is a read and write accessible register which controls the application of general diagnostic modes to the selected Auxiliary and/or CSA input paths.

|

| MXM_REG_BALSWCTRL | BALSWCTRL is a read and write accessible register which governs the behavior of the Charge Balancing Switches in Manual and Auto Cell Balancing modes.

Write access to this register is blocked during Automated Cell Balancing operations (CBMODE=001, 1xx).

|

| MXM_REG_BALEXP1 | BALEXPn is a read and write accessible register which holds the Cell Balancing Expiration Time for CELLn (using the switch across SWn and SWn-1).

BALEXP1 sets the Expiration Time for all Group Auto Cell Balancing and Discharge modes and the Watchdog time out for Manual Cell Balancing mode.

Write access to this register is blocked during all Cell Balancing operations (CBMODE!=000).

|

| MXM_REG_BALEXP2 | BALEXPn is a read and write accessible register which holds the Cell Balancing Expiration Time for CELLn (using the switch across SWn and SWn-1). Used in Individual Auto Cell Balancing modes only.

Write access to this register is blocked during Automatic Cell Balancing operations (CBMODE=1xx).

|

| MXM_REG_BALEXP3 | BALEXPn is a read and write accessible register which holds the Cell Balancing Expiration Time for CELLn (using the switch across SWn and SWn-1). Used in Individual Auto Cell Balancing modes only.

Write access to this register is blocked during Automatic Cell Balancing operations (CBMODE=1xx).

|

| MXM_REG_BALEXP4 | BALEXPn is a read and write accessible register which holds the Cell Balancing Expiration Time for CELLn (using the switch across SWn and SWn-1). Used in Individual Auto Cell Balancing modes only.

Write access to this register is blocked during Automatic Cell Balancing operations (CBMODE=1xx).

|

| MXM_REG_BALEXP5 | BALEXPn is a read and write accessible register which holds the Cell Balancing Expiration Time for CELLn (using the switch across SWn and SWn-1). Used in Individual Auto Cell Balancing modes only.

Write access to this register is blocked during Automatic Cell Balancing operations (CBMODE=1xx).

|

| MXM_REG_BALEXP6 | BALEXPn is a read and write accessible register which holds the Cell Balancing Expiration Time for CELLn (using the switch across SWn and SWn-1). Used in Individual Auto Cell Balancing modes only.

Write access to this register is blocked during Automatic Cell Balancing operations (CBMODE=1xx).

|

| MXM_REG_BALEXP7 | BALEXPn is a read and write accessible register which holds the Cell Balancing Expiration Time for CELLn (using the switch across SWn and SWn-1). Used in Individual Auto Cell Balancing modes only.

Write access to this register is blocked during Automatic Cell Balancing operations (CBMODE=1xx).

|

| MXM_REG_BALEXP8 | BALEXPn is a read and write accessible register which holds the Cell Balancing Expiration Time for CELLn (using the switch across SWn and SWn-1). Used in Individual Auto Cell Balancing modes only.

Write access to this register is blocked during Automatic Cell Balancing operations (CBMODE=1xx).

|

| MXM_REG_BALEXP9 | BALEXPn is a read and write accessible register which holds the Cell Balancing Expiration Time for CELLn (using the switch across SWn and SWn-1). Used in Individual Auto Cell Balancing modes only.

Write access to this register is blocked during Automatic Cell Balancing operations (CBMODE=1xx).

|

| MXM_REG_BALEXP10 | BALEXPn is a read and write accessible register which holds the Cell Balancing Expiration Time for CELLn (using the switch across SWn and SWn-1). Used in Individual Auto Cell Balancing modes only.

Write access to this register is blocked during Automatic Cell Balancing operations (CBMODE=1xx).

|

| MXM_REG_BALEXP11 | BALEXPn is a read and write accessible register which holds the Cell Balancing Expiration Time for CELLn (using the switch across SWn and SWn-1). Used in Individual Auto Cell Balancing modes only.

Write access to this register is blocked during Automatic Cell Balancing operations (CBMODE=1xx).

|

| MXM_REG_BALEXP12 | BALEXPn is a read and write accessible register which holds the Cell Balancing Expiration Time for CELLn (using the switch across SWn and SWn-1). Used in Individual Auto Cell Balancing modes only.

Write access to this register is blocked during Automatic Cell Balancing operations (CBMODE=1xx).

|

| MXM_REG_BALEXP13 | BALEXPn is a read and write accessible register which holds the Cell Balancing Expiration Time for CELLn (using the switch across SWn and SWn-1). Used in Individual Auto Cell Balancing modes only.

Write access to this register is blocked during Automatic Cell Balancing operations (CBMODE=1xx).

|

| MXM_REG_BALEXP14 | BALEXPn is a read and write accessible register which holds the Cell Balancing Expiration Time for CELLn (using the switch across SWn and SWn-1). Used in Individual Auto Cell Balancing modes only.

Write access to this register is blocked during Automatic Cell Balancing operations (CBMODE=1xx).

|

| MXM_REG_BALAUTOUVTHR | BALAUTOUVTHR is a read and write accessible register which selects the cell under voltage exit threshold for the ADC when used in Automated Cell Balancing operations.

A write to this register allows direct setting or automatic selection of this threshold.

Write access to this register is blocked during Automatic Cell Balancing operations (CBMODE=1xx). Also, during active measurement scans, all writes with CBUVMINCELL=1 will be blocked and will result in ALRTRJCT being issued (since the MINCELL data may be altered as a result of the scan in progress).

A read from this register will display the current value of the threshold and the method used for its selection.

|

| MXM_REG_BALDLYCTRL | BALDLYCTRL is a read and write accessible register which selects the delay/timing intervals used within Automated Cell Balancing operations.

Write access to this register is blocked during Automated Cell Balancing operations (CBMODE=001, 1xx).

|

| MXM_REG_BALCTRL | BALCTRL is a read and write accessible register which initiates and controls all internal Cell Balancing modes and operations.

Any write to this register to a mode other than CBMODE=000 (Disable) will restart the CBTIMER at zero and launch the requested mode of operation.

|

| MXM_REG_BALSTAT | BALSTAT is a read accessible register which allows the monitoring of any Automated Cell Balancing operations currently in progress.

Once a CBMODE is initiated, all status bits persist and are cleared only when CBMODE is written to 000 (Disabled) or when a new CBMODE operation is initiated via CBSTART.

|

| MXM_REG_BALUVSTAT | BALUVSTAT is a read accessible register which relates current summary information on the Cell voltages vs. the CBUVTHR undervoltage threshold.

|

| MXM_REG_BALDATA | BALDATA is a read accessible register which relates current summary information on the Cell voltage vs. the CBUVTHR undervoltage threshold.

|

| MXM_REG_I2CPNTR | MAX17852 only: I2CPNTR is a read and write accessible register which contains two Pointer bytes (Register Addresses) available for I2C Master transactions.

Once I2CSEND initiates a read or write transaction, attempts to write I2CPNTR during the transaction will be ignored and will case an I2CRJCT fault to be issued.

|

| MXM_REG_I2CWDATA1 | MAX17852 only: I2CWDATA1 is a read and write accessible register which contains the upper data bytes available for I2C Master Write Mode transactions.

Once I2CSEND initiates an I2C read or write transaction, attempts to write I2CWDATA1 during the transaction will be ignored and will cause an I2CRJCT fault to be issued.

|

| MXM_REG_I2CWDATA2 | MAX17852 only: I2CWDATA2 is a read and write accessible register which contains the lower data bytes available for I2C Master Write Mode transactions.

Once I2CSEND initiates an I2C read or write transaction, attempts to write I2CWDATA2 during the transaction will be ignored and will cause an I2CRJCT fault to be issued.

|

| MXM_REG_I2CRDATA1 | MAX17852 only: I2CRDATA1 is a read accessible register which contains the upper data bytes received for I2C Master Read Mode transactions.

Note during I2C read transactions, data is updated as each byte is received/acknowledged, so reading back this register during active I2C read transactions will cause an I2CRJCT fault to be issued.

|

| MXM_REG_I2CRDATA2 | MAX17852 only: I2CRDATA2 is a read accessible register which contains the lower data bytes received for I2C Master Read Mode transactions.

Note during I2C read transactions, data is updated as each byte is received/acknowledged, so reading back this register during active I2C read transactions will cause an I2CRJCT fault to be issued.

|

| MXM_REG_I2CCFG | MAX17852 only: I2CCFG is a read and write accessible register which configures I2C Master modes and transaction formats.

Once I2CSEND initiates a read or write transaction, attempts to write I2CCFG during the transaction will be ignored and will cause and I2CRJCT fault to be issued.

|

| MXM_REG_I2CSTAT | MAX17852 only: I2CSTAT is a read and write accessible register which shows the current status of the I2C Master.

The I2CSTATUS bits are updated in real time, indicating the current state of the I2C Master and any requested transaction. This status can be cleared by write operations and modified by transaction progress or subsequent transaction requests.

The second byte contains I2C Fault bits, indicating a fault was observed during an I2C transaction. These bits are updated as they occur and are only cleared by writing to zero. Several faults may occur during a corrupted transaction, so it is best to wait until I2CSTATUS reads 10 (Transaction Error) to ensure all errors have been reported.

While not advisable, if further I2C transactions are requested before the I2C Fault bits from previous transactions are read back and cleared, a cumulative history of faults will be listed, even if subsequent transactions are successful.

|

| MXM_REG_I2CSEND | MAX17852 only: I2CSEND is a read and write accessible register which configures and initiates an I2C Master transaction.

A write to this register will initiate an I2C Master transaction. Only one transaction is supported at any given time. If a write to I2CSEND occurs during an active I2C transaction already in progress, the latest transaction request will be ignored and the I2CSEND contents will not be updated. If this occurs, an I2CRJCT fault will be issued.

A read from this register will readback the current contents. This will represent the last transaction request accepted by the I2C Master.

|

| MXM_REG_ID1 | ID1 is a read accessible register which contains the 2 LSBytes of the unique Device ID stored in ROM and subject to ROMCRC validation.

|

| MXM_REG_ID2 | ID2 is a read accessible register which contains the 2 MSBytes of the unique Device ID stored in ROM and subject to ROMCRC validation.

|

| MXM_REG_OTP2 | Factory Calibration Data ROM and subject to ROMCRC validation.

|

| MXM_REG_OTP3 | Factory Calibration Data ROM and subject to ROMCRC validation.

|

| MXM_REG_OTP4 | Factory Calibration Data ROM and subject to ROMCRC validation.

|

| MXM_REG_OTP5 | Factory Calibration Data ROM and subject to ROMCRC validation.

|

| MXM_REG_OTP6 | Factory Calibration Data ROM and subject to ROMCRC validation.

|

| MXM_REG_OTP7 | Factory Calibration Data ROM and subject to ROMCRC validation.

|

| MXM_REG_OTP8 | Factory Calibration Data ROM and subject to ROMCRC validation.

|

| MXM_REG_OTP9 | Factory Calibration Data ROM and subject to ROMCRC validation.

|

| MXM_REG_OTP10 | Factory Calibration Data ROM and subject to ROMCRC validation.

|

| MXM_REG_OTP11 | Factory Calibration Data ROM and subject to ROMCRC validation.

|

| MXM_REG_OTP12 | Factory Calibration Data ROM and subject to ROMCRC validation.

|